Computation Structures

**Sequential Logic Worksheet**

# **Concept Inventory:**

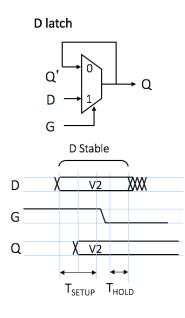

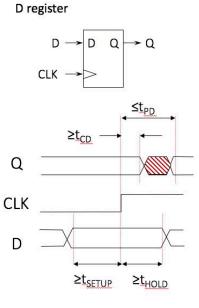

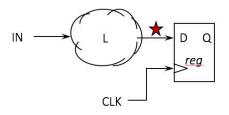

- D-latch & the Dynamic Discipline

- D-register

- Timing constraints for sequential circuits

- Set-up and hold times for sequential circuits

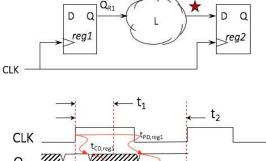

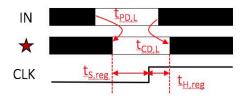

- $t_1 = t_{CD,reg1} + t_{CD,L} \ge t_{HOLD,reg2}$

- $t_2 = t_{PD,reg1} + t_{PD,L} + t_{SETUP,reg2} \le t_{CLK}$

# Problem 1.

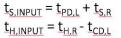

Consider the following sequential logic circuit. It consists of one input IN, a 2-bit register that stores the current state, and some combinational logic that determines the state (next value to load into the register) based on the current state and the input IN.

(A) Using the timing specifications shown below for the XOR and DREG components, determine the shortest clock period,  $t_{CLK}$ , that will allow the circuit to operate correctly or write NONE if no choice for  $t_{CLK}$  will allow the circuit to operate correctly and briefly explain why.

| Component | $t_{CD}$ | $t_{PD}$ | <i>t</i> <sub>SETUP</sub> | t <sub>HOLD</sub> |

|-----------|----------|----------|---------------------------|-------------------|

| XOR2      | 0.15ns   | 2.1ns    | _                         | —                 |

| DREG      | 0.1ns    | 1.6ns    | 0.4ns                     | 0.2ns             |

Minimum value for t<sub>CLK</sub> (ns): \_\_\_\_\_\_ or explain why none exists

(B) Using the same timing specifications as in (A), determine the setup and hold times for IN with respect to the rising edge of CLK.

t<sub>SETUP</sub> for IN with respect to CLK<sup>↑</sup> (ns): \_\_\_\_\_

t<sub>HOLD</sub> for IN with respect to CLK<sup>↑</sup> (ns): \_\_\_\_\_

(C) One of the engineers on the team suggests using a new, faster XOR2 gate whose  $t_{CD} = 0.05$ ns and  $t_{PD} = 0.7$ ns. Determine a new minimum value for  $t_{CLK}$  or write NONE and explain why no such value exists.

Minimum value for t<sub>CLK</sub> (ns): \_\_\_\_\_\_ or explain why none exists

#### Problem 2.

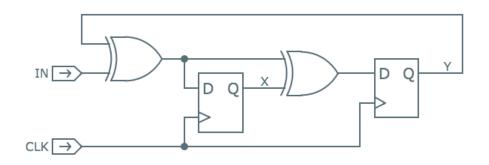

Consider the following sequential logic circuit. It consists of three D registers, three different pieces of combinational logic (CL1, CL2, and CL3), one input IN, and one output OUT. The propagation delay, contamination delay, and setup time of the registers are all the same and are specified below each register. The hold time for the registers is NOT the same and is specified in bold below each register. The timing specification for each combinational logic block is shown below that logic.

(A) (1 point) What is the smallest value for the t<sub>CD</sub> of CL2 that will guarantee the dynamic discipline is obeyed for all the registers in the circuit?

Smallest value for t<sub>CD</sub> of CL2 (ns): \_\_\_\_\_

(B) (2 points) What is the smallest value for the period of CLK (i.e., t<sub>CLK</sub>) that will guarantee the dynamic discipline is obeyed for all the registers in the circuit?

Smallest value for t<sub>CLK</sub> (ns): \_\_\_\_\_

(C) (2 points) What are the smallest values for the setup and hold times for IN relative to the rising edge of CLK that will guarantee the dynamic discipline is obeyed for all the registers in the circuit?

Setup time for IN (ns): \_\_\_\_\_

Hold time for IN (ns): \_\_\_\_\_

(D) (2 points) What are the propagation delay and contamination delay of the output, OUT, of this circuit relative to the rising edge of the clock?

t<sub>PD</sub> for OUT (ns): \_\_\_\_\_

t<sub>CD</sub> for OUT (ns): \_\_\_\_\_

# Problem 3.

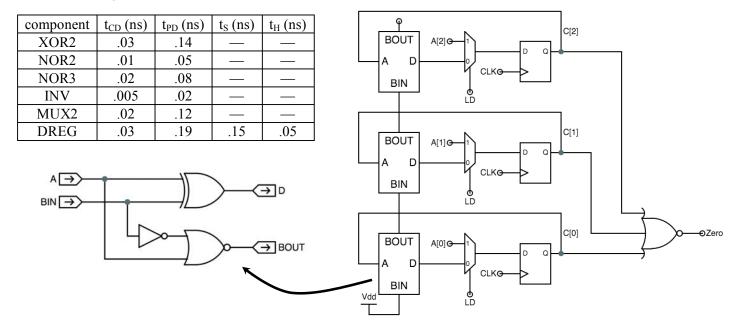

Here's a schematic for a 3-bit loadable down-counter, which uses a ripple decrementer as a building block:

(A) Using the contamination delays (t<sub>CD</sub>), propagation delays (t<sub>PD</sub>), setup times (t<sub>S</sub>), and hold times (t<sub>H</sub>) shown in the table above, please compute the minimum value for the clock period (t<sub>CLK</sub>) for which the circuit will work correctly.

minimum value for t<sub>CLK</sub> (ns): \_\_\_\_\_

(B) What are the appropriate values for the setup  $(t_s)$  and hold  $(t_H)$  times for the LD input with respect to the rising edge of the clock?

setup time (t<sub>s</sub>) for LD: \_\_\_\_\_

hold time (t<sub>H</sub>) for LD: \_\_\_\_\_

(C) What is the  $t_{PD}$  for the Zero output with respect to the rising edge of CLK?

t<sub>PD</sub> for Zero (ns): \_\_\_\_\_

# Problem 4.

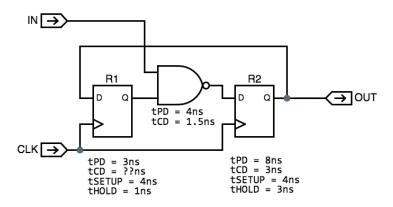

Consider the following sequential logic circuit. The timing specifications are shown below each component. Note that the two registers do NOT have the same specifications.

(A) What are the smallest values for the setup and hold times for IN relative to the rising edge of CLK that will guarantee the dynamic discipline is obeyed for all the registers in the circuit?

Setup time for IN (ns): \_\_\_\_\_

Hold time for IN (ns): \_\_\_\_\_

(B) What is the smallest value for the period of CLK (i.e., tCLK) that will guarantee the dynamic discipline is obeyed for all the registers in the circuit?

Smallest value for tCLK (ns): \_\_\_\_\_

(C) What is the smallest for the tCD of R1 that will guarantee the dynamic discipline is obeyed for all the registers in the circuit?

Smallest value for tCD of R1 (ns): \_\_\_\_

(D) Suppose two of these sequential circuits were connected in series, with the OUT signal of the first circuit connected to the IN signal of the second circuit. The same CLK signal is used for both circuits. Now what is the smallest value for the period of CLK (i.e., tCLK) that will guarantee the dynamic discipline is obeyed for all the registers in the circuit?

Smallest value for tCLK (ns): \_\_\_\_\_

# Problem 5.

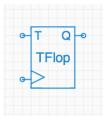

It is often useful to make clocked devices that count in binary, and a simple building block for such binary counters is the toggle flipflop whose symbol is shown on the right. It is a clocked device, hence the clock input indicated by the triangle on its lower-left edge. The other input, T (for *toggle*), may be set to one to cause the TFlop to flip its state (the Q output) from 0 to 1 or vice versa on the next active (positive)

ps

clock edge. If T is zero at an active clock edge, the state of the TFlop remains unchanged. We assume that the initial state of each TFlop at power-up is Q=0; more sophisticated versions might feature a *Reset* input to force a Q=0 state.

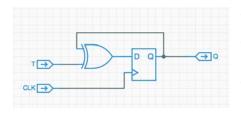

A TFlop may be implemented using a D flipflop like the ones developed in lecture together with an XOR2 gate, as shown to the left.

As is our convention for clocked devices, we would like to specify timing specs for the TFlop as  $t_{CD}$ ,  $t_{PD}$ ,  $t_{SETUP}$ , and  $t_{HOLD}$ , all measured relative to the active (positive) clock edge.

t<sub>CD</sub>:

(A) The timing specifications for the components are shown in the table below. Give appropriate values for the timing specifications of the TFlop implementation shown above.

| ps  |

|-----|

|     |

| _ps |

|     |

| _ps |

|     |

(B) Suppose we connect the T input of a single TFlop to 1 (i.e.,  $V_{DD}$ ) and try to clock it at its maximum rate. What is the minimum clock period we can use and expect the TFlop to perform properly?

# Minimum clock period for correct operation: ps

We next consider the use of four TFlops to make a 4-bit ripple-carry counter as shown to the left. Assume that the TFlops share a common clock input (not shown) with an appropriate period, and that all TFlops have an initial Q=0 state.

(C) Suppose we run this circuit for a large number, N, of clock cycles. For approximately how many of the N active clock edges would you expect the T input to the topmost TFlop to be 1?

# Topmost T=1 occurrences in N cycles: \_\_\_\_\_

(D) If the AND2 gates have  $t_{PD}$  =200ps and  $t_{CD}$  =40ps, what is the minimum clock period we can use for the 4-bit counter?

Minimum clock period for correct operation: \_\_\_\_\_ps

MIT OpenCourseWare <a href="https://ocw.mit.edu/">https://ocw.mit.edu/</a>

6.004 Computation Structures Spring 2017

For information about citing these materials or our Terms of Use, visit: <u>https://ocw.mit.edu/terms</u>.