Computation Structures **CMOS Technology Worksheet**

# **Concept Inventory:**

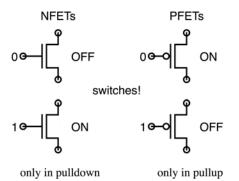

- PFET, NFET: voltage controlled switches

- CMOS composition rules: complementary pullup and pulldown

- CMOS gates are naturally inverting

- t<sub>PD</sub> and t<sub>CD</sub> timing specifications

- Lenient gates

#### Notes:

We want *complementary* pullup and pulldown logic, i.e., the pulldown should be "on" when the pullup is "off" and vice versa.

|          |                 | Power supply                                     |

|----------|-----------------|--------------------------------------------------|

| pulldown | F(inputs)       | Pullup                                           |

| off      | driven "1"      | → circuit                                        |

| on       | driven "0"      | inputs output                                    |

| on       | driven "X"      | $\rightarrow$ Pulldown circuit                   |

| off      | no connection   | Ground                                           |

|          | off<br>on<br>on | off driven "1"<br>on driven "0"<br>on driven "X" |

## CMOS gates are naturally inverting:

- Rising input (0 to 1): NFETs turn on, PFETs turn off; if output changes, it falls (1 to 0)

- Falling input (1 to 0): NFETs turn off, PFETs turn on; if output changes, it rises (0 to 1)

## Timing:

٠

- t<sub>PD</sub> (propagation delay): how long after inputs are stable and valid until outputs are stable and valid = max over all paths from input to output (sum of component t<sub>PD</sub> along path)

- t<sub>PD</sub> specification is an upper bound on all measured propagation delays

- t<sub>CD</sub> (contamination delay): how long output stays valid after inputs go invalid =

- min over all paths from input to output (sum of component t<sub>CD</sub> along path)

- $\circ$  t<sub>CD</sub> specification is a lower bound on all measured contamination delays

## Lenient gate:

- If a subset of a lenient gate's inputs is suffice to guarantee an specific output value (i.e., the values of the other inputs don't matter in this case), then the output will remain valid and stable by transitions on the irrelevant inputs.

- CMOS gates are naturally lenient

| NOR: A B Z                                                           | Lenient | ABZ            | A |

|----------------------------------------------------------------------|---------|----------------|---|

| $\begin{array}{ccc} 0 & 0 & 1 \\ 0 & 1 & 0 \\ 1 & 0 & 0 \end{array}$ | NOR:    | 0 0 1<br>X 1 0 | B |

| $\begin{array}{c c}1 & 0 & 0\\1 & 1 & 0\end{array}$                  |         | 1 X 0          | Z |

# Problem 1.

(A) Which of the above CMOS pulldown circuits would implement F if the corresponding complementary pullup circuit was also provided? For each pulldown, select Yes if it is a valid pulldown for F, and No if it is not a valid pulldown for F.

| PD1 (Yes/No): | F |

|---------------|---|

| PD2 (Yes/No): |   |

| PD3 (Yes/No): |   |

| PD4 (Yes/No): | ┝ |

| PD5 (Yes/No): | F |

|               |   |

|               |   |

|               |   |

|               |   |

| Α | В | C | D | F |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 |

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

(B) Are all the implementations you selected for part (A) lenient?

All lenient (Yes/No): \_\_\_\_\_

# Problem 2.

(A) A single CMOS gate, consisting of an output node connected to a single PFET-based pullup circuit and a single NFET-based pulldown circuit (as described in lecture) computes F(A, B, C, D). It is observed that F(1, 0, 1, 0) = 1. What can you say about the following values?

(circle one) F(0, 0, 1, 0) = : 0 ... 1 ... (can't say)

(circle one) F(1, 1, 1, 0) = : 0 ... 1 ... (can't say)

(circle one) F(1, 1, 1, 1) = : 0 ... 1 ... (can't say)

(B) The Boolean function F(A,B,C) can be implemented using a *single* CMOS gate operating as a combinational device that obeys the static discipline. It's known that F(1,1,0) = 1 and F(0,1,1) = 0. What can be determined about the value of F in the following cases? Please circle one of "0", "1" or "Can't tell".

| (circle one) F(1,0,0) = | 0 | ••• | 1 | ••• | Can't tell |

|-------------------------|---|-----|---|-----|------------|

| (circle one) F(1,0,1) = | 0 | ••• | 1 | ••• | Can't tell |

| (circle one) F(1,1,1) = | 0 | ••• | 1 | ••• | Can't tell |

(C) A single CMOS gate, consisting of an output node connected to a single pullup circuit containing one or more PFETs and a single pulldown circuit containing one or more NFETs (as described in lecture), computes F(A,B). F has the property that for all A,  $F(A,0) = \overline{F(A,1)}$ . What can you say about the value of F(1,0)?

(circle one):  $F(1,0) = 1 \dots 0 \dots$  can't tell

# Problem 3.

For each of the functions F and G, if the function can be implemented using a **single CMOS gate**, please draw the corresponding single CMOS gate. If it cannot be implemented using a single CMOS gate, then write NONE. For full credit use a minimum number of FETs.

| Α | B | C | F | G |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 |

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 1 | 0 |

| Draw CMOS implementation of<br>F(A,B,C) below or write NONE if<br>F cannot be implemented as single<br>CMOS gate. | Draw CMOS implementation of<br>G(A,B,C) below or write NONE if<br>G cannot be implemented as single<br>CMOS gate. |

|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|

|                                                                                                                   |                                                                                                                   |

|                                                                                                                   |                                                                                                                   |

|                                                                                                                   |                                                                                                                   |

|                                                                                                                   |                                                                                                                   |

## Problem 4.

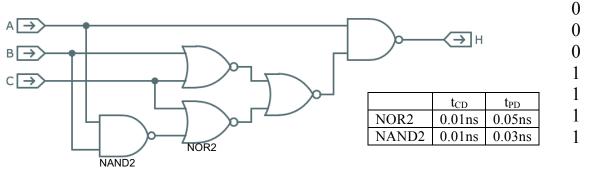

Consider the Boolean function that has the truth table shown to the right; a possible implementation as a combinational circuit is shown in the schematic below. You may assume that the NOR2 and NAND2 components are combinational.

(A) Using the timing specifications shown above for NOR2 and NAND2, compute the contamination and propagation delay for the implementation of H shown above.

timing for H (ns):  $t_{CD}$ =\_\_\_\_\_  $t_{PD}$ =\_\_\_\_\_

(B) Can H be implemented as a single CMOS gate (only PFETs in the pullup circuit, only NFETs in the pulldown circuit)? If so draw the MOSFET schematic for H to the right, otherwise write "NO".

## Draw schematic or write "NO"

## Problem 5.

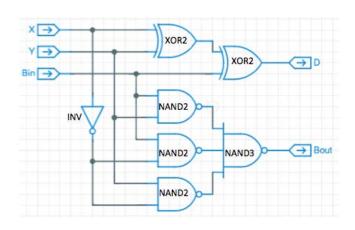

A gate-level schematic is shown below. Using the  $t_{CD}$  and  $t_{PD}$  information for the gate components shown in the table below, compute  $t_{CD}$  and  $t_{PD}$  for the circuit.

## **Compute timing specs:**

Η

1

0

B C

0

0 1 1

1

1 1 1

0 0 1

$0 \ 1 \ 0$

1 0 1

1

0 1

0

1

А

0

$t_{PD} = \underline{ns}$

| Gate  | t <sub>CD</sub> | t <sub>PD</sub> |

|-------|-----------------|-----------------|

| INV   | 0.1ns           | 1.0ns           |

| NAND2 | 0.2ns           | 1.5ns           |

| NAND3 | 0.3ns           | 1.8ns           |

| XOR2  | 0.6ns           | 2.5ns           |

# Problem 6.

A minority gate has three inputs (call them A, B, C) and one output (call it Y). The output will be 0 if two or more of the inputs are 1, and 1 if two or more of the inputs are 0.

In the space below, draw the *pulldown* circuit for a single CMOS gate that implements the minority function, using the minimum number of NFETs. You needn't draw the *pullup* circuit.

If you're convinced that the function cannot be implemented as a single CMOS gate, give a brief, convincing explanation.

## Can it be implemented as single CMOS gate? Circle one: YES can't tell NO

# Problem 7.

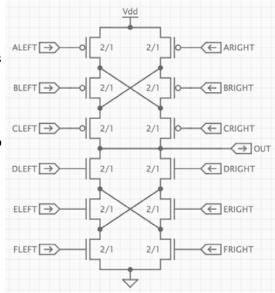

In his bid for the Lemelson Prize, Ben Bitdiddle has invented the "flexible gate," a single CMOS gate that implements different functions depending how its inputs are wired up. The FlexGate® (see figure at right) uses 6 PFETs in its pullup circuit and 6 NFETs in its pulldown circuit.

Each of the FlexGate's twelve inputs can connected to an input signal (X, Y, ...), GND (logical "0") or VDD (logical "1"). To show off its versatility, Ben has asked you to show how to hook up the inputs so the FlexGate computes several different functions whose Boolean equations are given below. Associated with each equation is a table with 12 entries; in each cell of the table please write an input name, GND or VDD as appropriate. Note that there may be several possible implementations for each of the three functions – any correct answer will be acceptable. Hint: there should be an entry in each cell, i.e., a connection should be specified each input!

Fill in tables below or mark with "X"

| OUT = | $X \cdot Y$ |

|-------|-------------|

|-------|-------------|

| input | LEFT | RIGHT |

|-------|------|-------|

| А     |      |       |

| В     |      |       |

| С     |      |       |

| D     |      |       |

| Е     |      |       |

| F     |      |       |

$OUT = \overline{X + Y + Z}$

| input | LEFT | RIGHT |

|-------|------|-------|

| А     |      |       |

| В     |      |       |

| С     |      |       |

| D     |      |       |

| E     |      |       |

| F     |      |       |

| OUT = | $\overline{X}$ + | Y | Z |

|-------|------------------|---|---|

|       |                  | - |   |

| input | LEFT | RIGHT |

|-------|------|-------|

| А     |      |       |

| В     |      |       |

| С     |      |       |

| D     |      |       |

| Е     |      |       |

| F     |      |       |

# Problem 8.

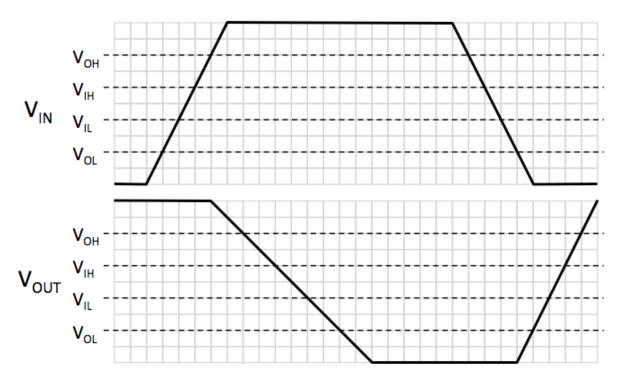

The response of a combinational gate to a test input waveform is shown below. Each horizontal division of the plot represents 10 ps.

(A) Based on the figure below, what is an appropriate choice for the contamination delay of the gate?

(B) Based on the figure below, what is an appropriate choice for the propagation delay of the gate?

MIT OpenCourseWare <a href="https://ocw.mit.edu/">https://ocw.mit.edu/</a>

6.004 Computation Structures Spring 2017

For information about citing these materials or our Terms of Use, visit: <u>https://ocw.mit.edu/terms</u>.